2023. 4. 21. 17:22ㆍ전자회로 해석 및 설계

오실로스코프를 신호에 연결하였을때, 오실로스코프의 입력 저항은 1M옴이다.

프로브의 선택 단자를 1x, 10x로 변경함으로써 입력측 저항을 변경할 수 있다. 이렇게 입력측 저항을 변경할 수 있도록 만든 이유는 회로의 저항이 k단위일때는 1:1모드로 놓고도 잘 측정할 수 있지만, 만약 회로측 저항과 오실로스코프의 입력저항이 크게 차이나지 않을 경우에는 내부저항과 입력저항이 병렬로 연결되어 Load Effect가 발생한다.

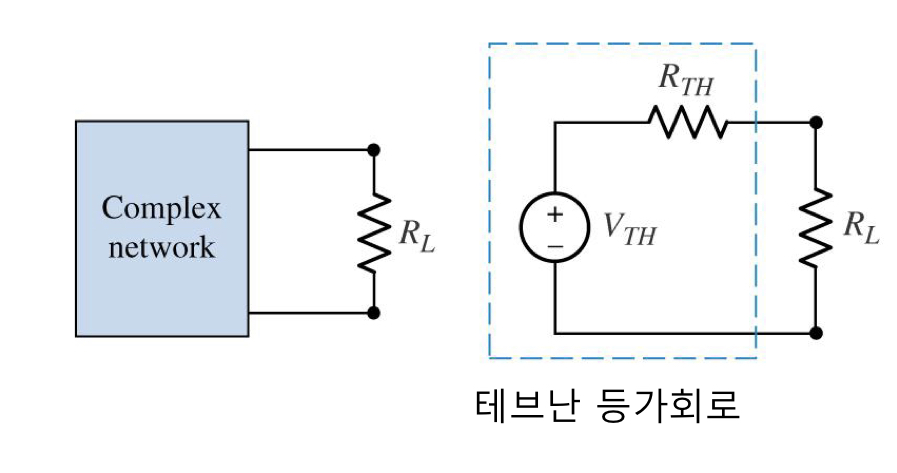

등가 회로

- 서로 다른 두 회로의 특정 단자에서 본 전압이 같을 경우에 두 회로를 등가 회로이다.

- 내부 회로가 같은 경우가 아닌 어떤 단자에서 봤을 때 전기적인 특성이 같아야 한다.

- A B, A' B' 단자를 모두 개방시켜놓고 전압을 측정한다.

- 두 회로의 단자를 모두 단락시켜놓고 전류를 측정한다.

등가 회로는 전기적인 특성이 같기 때문에 복잡한 회로의 간단한 등가회로를 만들어 전기적인 특성을 쉽게 계산할 수 있다.

등가 회로는 크게 두 가지가 있다.

테브난 등가회로

- 부하 저항을 제외한 회로의 모든 소자를 한 개의 전압원과 직렬 연결로 대체한다. 이때 부하저항에서 측정한 응답은 동일하다.

노턴 등가회로

- 부하 저항을 제외한 모든 수자를 한개의 전류원과 병렬 연결로 대체한다. 테브난 등가회로와 상호 변환 할 수 있다.

등가회로 구하기

테브난 등가회로를 구하려면 부하저항에서 들여다본 내부 저항을 구한다. 전압원은 단락시키고 테브닌 등가저항과 테브닌 등가 전압을 구한다. 부하저항에서 들여다본 내부저항을 구한다는 의미는 내부에 있는 모든 전원을 없애고 부하저항 쪽에서 테스트전압을 달아 테스트 전류를 구한다고 생각하면 된다. 전압원은 단락, 전류원은 개방시키고 등가저항을 구한다.

등가저항에 흐르는 전류와 걸린 전압이 테브난 등가전압, 녹턴 등가전류이다.

등가저항을 찾기 어렵다면 테스트 전원을 연결하면, 등가저항을 쉽게 구할 수 있다. 위에서 등가저항은 3/1ma = 3k이다.

시뮬레이션으로 보면 전기적 특성이 동일한 것을 볼 수 있다.

최대전력공급조건

시뮬레이션으로 확인하는 방법은 다음과 같다.

최대 전력조건은 두 저항의 값이 같은 100옴일 때 부하저항에 최대 전력이 걸리는 것을 볼 수 있다. 최대전력은 25W이다.

위의 회로에서, RF 단의 저항에서 가장 왜곡이 적은 임피던스는 75옴이고, 전력이 가장 많이 전달되는 33옴이다.

어떤 앰프의 출력 임피던스가 8옴이라면, 스피커의 저항도 8옴이어야 파형이 잘 전달된다. 이러한 과정을 매칭이라고 한다.

정현파

- 각속도 : 1초동안 회전한 각도. [rad/sec]

- 1초동안 Rad만큼 회전했을때의 각 속도

위상 표현은 하나의 정현파를 비교하는데 의미가 없다.

시뮬레이션 화면을 보면 계산 간격이 너무 커서 고르지 못한 파형이 나왔다. 계산 간격을 조정할 수 있다. 파형의 주기의 1000분의 1정도 계산 주기를 주면 깔끔하게 나온다.

DF항목을 조정하면 아래와 같은 함수로 표현할 수 있다.

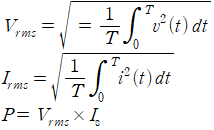

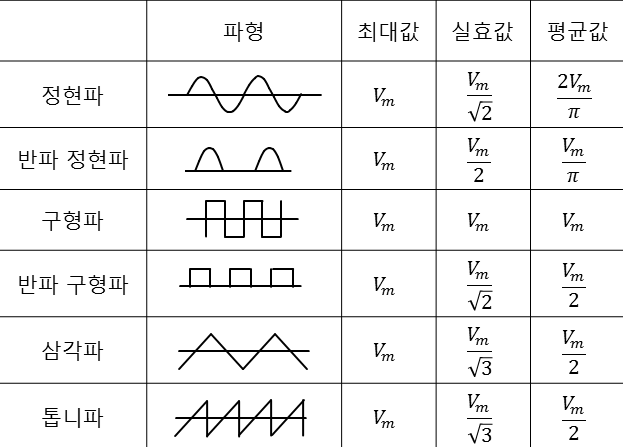

실효값

- 교류를 이용해 직류와 동일한 열량을 발생시킬 때의 값

- 대부분의 전류계, 전압계는 실효값을 지시

교류전력의 평균 전력을 계산하는 방법은, 전력을 0부터 T까지 적분한다음 T로 나누어주면 된다.

그러나 이렇게 계산하면 어렵기 때문에, 교류값을 직류처럼 계산하기위해 RMS값을 사용한다.

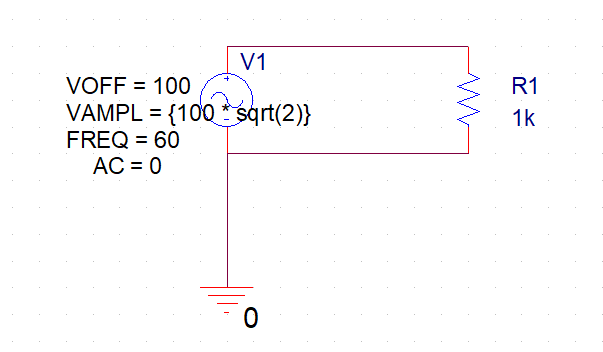

100V의 DC전압이 R1에 하는 일은 10W이다. 그렇다면 위의 R1의 전력은 몇일까? DC와 AC가 각각 10W씩 공급하므로 20W를 공급하게된다.

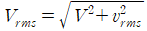

우리가 사용하는 대부분의 멀티미터는 순수한 교류파형에 대한 RMS값만 측정해준다. DC와 AC가 중첩되어있는 신호에 대해서는 측정하지 못한다. 따라서 멀티미터를 DC모드로 측정하고, AC모드로 측정하고, 위의 식을 이용해 rms값을 구해줘야한다.

구형파

펄스 : 단발적으로 한번만 나오는 파형을 Pulse라고 한다.

펄스파 : 위의 Pulse가 규칙적 또는 불규칙적으로 반복적으로 나오는 파형

상승 시간 : 최대값의 10%에서 90%까지 올라가는데 걸리는 시간

하강 시간 : 최대값의 90%에서 10%까지 올라가는데 걸리는 시간

지연 시간 : 최대값의 50%까지 올라가는데 걸리는 시간

펄스 폭 : 상승할때 최대값의 50% 지점에서 하강할때 50%지점까지 걸린 시간

듀티 사이클 : 펄스 폭 / 한 주기 * 100

펄스 신호는 아날로그 신호라고 한다.

크기는 낮다 높다밖에 없지만, 펄스의 폭 부분을 연속적으로 조절할 수 있기 때문이다.

시뮬레이션에서는 최대값의 0 ~ 100%까지 올라가는데 걸리는 시간으로 이용된다.

'전자회로 해석 및 설계' 카테고리의 다른 글

| 전자회로 해석 및 설계 7일차 (0) | 2023.05.19 |

|---|---|

| 전자회로 해석 및 설계 6일차 (0) | 2023.05.15 |

| 전자회로 해석 및 설계 - 4일차 (0) | 2023.05.09 |

| 전자회로 해석 및 설계 3일차 L, C (0) | 2023.04.24 |

| 전자회로 해석 및 설계 1일차 (0) | 2023.04.17 |