2023. 5. 9. 14:04ㆍ전자회로 해석 및 설계

- 수동필터의 종류와 특성

- 통과 대역 별

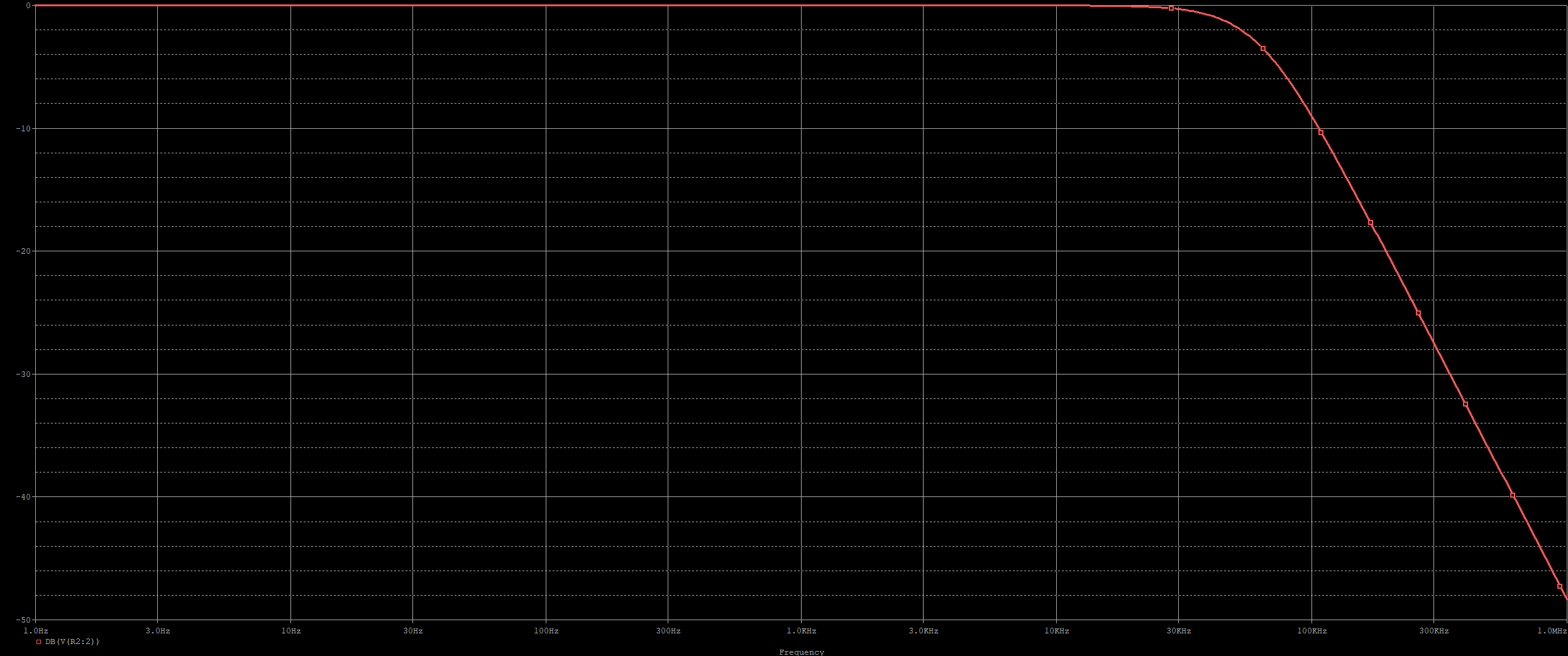

- LPF(Low Pass Filter) : 저역통과필터

- HPF(High Pass Filter) : 고역통과필터

- BPF(Band Pass Filter) : 대역통과필터

- BRF(Band Reject Filter) : 대역차단필터

- 적용 소자 별

- Passive Filter : RLC수동소자로만 구성

- Active Filter : RLC + 능동 소자(트랜지스터, Op-Amp)

- 필터의 차수 별

- 1차 : L 또는 C가 1개만 있을 경우

- 2차 : L혹은 C가 2개만 있을 경우

- 3차 : L 또는 C가 3개만 있을 경우

- 통과 대역 별

필터의 차수가 높아질수록 Ideal 한 필터에 가까워진다. 보통은 1 또는 2차 필터를 사용한다.

- 공진주파수 :X_l과 X_c가 같아지는 주파수

공진이 되면 C하고 L의 임피던스가 0에 가까운 상태가 되어 R밖에 생기지 않는다. R은 이러한 회로를 안정화시키는 데 사용된다.

높은 주파수에서, 캐퍼시터는 RLC직렬 구조처럼 동작한다. 따라서 오른쪽의 그래프는 고주파에서 캐퍼시터의 임피던스 구조와 비슷하다.

ESR : RLC 등가 모델에서 R성분

ESL : RLC 등가 모델에서 L성분

위 2개는 캐퍼시터의 구조, 재료에서 나오는 기생 R, L값이다.

공진 주파수에서 L과 C의 임피던스가 무한대로 커진 상태가 되어 OPENED 회로와 비슷해진다.

저항의 고주파 모델

저항도 캐퍼시터와 마찬가지로 구조와 재료때문에 ESR, ESL이 생기게 된다.

SMD 타입 저항은 PCB 뒷면에도 붙일 수 있다. 따라서 양면으로 PCB를 만들 수 있다.

100 Mhz정도의 회로에서 DIP타입 저항의 그래프 특성이 점점 망가지는 것을 볼 수 있다.

어떤 저항의 정격저항이 1W라고 할 때, 70도까지는 1W까지 버티지만, 온도가 올라갈수록 견딜 수 있는 전력이 줄어든다.

이 때문에 회로를 설계할 때 이론적으로는 50% 정도의 여유를 줘야 한다. 실제로는 20~30% 정도의 여유를 준다.

ESL이 변화됐을 때, V의 그래프

디커플링 캐퍼시터

디커블링 캐퍼시터를 달지 않으면 도선 내부의 L 때문에 IO단에 전압강하가 생긴다. 이를 줄이기 위해 캐퍼시터를 전원단과 병렬로 연결하면 전압 강하가 줄어든다.

캐퍼시터를 달지 않았을 경우 3.4V까지 전압강하가 일어나지만, 캐퍼시터를 달면 아래와 같이 전압강하가 줄어든다.

전압강하가 4.95V로 훨씬 줄어든 모습을 볼 수 있다. 이 때, 고주파수인 상황이므로 전해 캐패시터보다는 MLCC를 사용하는 게 좋다.

GND단에도 마찬가지로, 도선의 기생 인턱터 때문에 전압이 위로 튀게 된다. GND 쪽은 캐퍼시터를 달 수 없기 때문에 이를 해결하려면 GND단의 기생 L값을 작게 만들어주는 수밖에 없다. 기생 L값을 줄이려면, GND 쪽의 선을 짧고 넓게 그려야 한다. 선을 넓게 그리면 기생 L이 병렬연결 되어 있는 것처럼 생성되고, 선을 길게 그리면 직렬연결 되어 있는 것처럼 생성된다. 그래서 PCB회로를 그릴 때 GND단을 넓게 그린다.

인덕터의 고주파 모델

인덕터의 고주파 등가 모델은 RLC 병렬 형태로 나오게 된다.

DCR : 구리선 자체의 저항 성분(DC입장에서 봤을 때 저항 성분)

인덕터에서 전류를 흘리면 자속이 증가하지만, 인덕터가 만들 수 있는 자속의 한계를 넘어서는 전류가 흐르면, 자속이 감소해버린다. 이때 자속이 30% 감소했을 때의 전류를 IDC1 또는 DCI1이라고 한다.

인덕터도 열에 따라 소자의 특성이 변하는데, 전류가 흐를수록 온도가 높아진다. 이 때 인덕터의 내열 한계일 때 흐르는 전류를 IDC2 또는 DCI2라고 한다.

비즈

- L || C 공진영역에서의 저항특성을 이용해서 Noise를 제거하는 부품

- 비즈의 등가모델은 L, R , C의 병렬 회로와 하나의 저항이 직렬 연결되어 있는 모델이다.

DC는 L을 통해서 작은 저항인 R2를 통과한다. 즉 거의 저항이 없는 Short circuit 으로 보인다.

주파수가 증가하면 인덕터의 저항 성분이 증가하고, 주파수가 LC공진 주파수가 되면 L과 C는 Open Circuit으로 보인다. 그때는 비즈는 마치 R1 + R2인 직렬 저항 회로로 작동한다.

공진 주파수보다 더 크게 되면 캐퍼시터의 임피던스는 감소할 것이다. 그 때는 캐퍼시터를 통해서 전류가 흐를 것이다.

이 때는 마치 캐퍼시턴스와 R2가 직렬연결된 회로처럼 보일 것이다.

비즈의 임피던스는 100Mhz일 때 기준으로 측정한다.

비즈는 코일을 이용해 만들기 때문에 오차가 크다.

비즈는 직렬로 연결하기 때문에 전류 스펙이 중요하다.

비즈를 달면 다음과 같이 전압이 튀는 현상이 없어진다.

Diode

다이오드는 실리콘에 3가 원소를 넣어 만든 P형 반도체와 실리콘데 5가 원소를 넣어 만든 N형 반도체를 접합시켜 만든다.

이렇게 P와 N반도체를 접합시키면 접합시키는 부위에 공핍층이 생긴다.

P부분에 +전압을 연결해 주는 것을 순방향 바이어스, N부분에 +전압을 연결해 주는 것을 역방향 바이어스라고 한다.

역방향 바이어스를 걸어주면 다음과 같은 일이 일어난다.

- 공핍층 확대

- N형 반도체의 전자들은 전압원의 +쪽으로 이동하고, P형 반도체의 정공도 전압원의 -쪽으로 이동한다.

- 소수 캐리어에 의한 전류인 역포화전류만 발생한다. (전류가 거의 흐르지 않는다)

- 항복 전압 이상의 전압을 걸어주면 역방향(음극에서 양극)으로 엄청나게 큰 전류가 흐르면서 다이오드가 망가진다.

순방향 바이어스를 걸어주면 다음과 같은 일이 일어난다.

- 공핍층이 줄어든다.

- 다수 캐리어(P형 - 정공, N형 - 전자)가 접합부를 가로질러 흐르게 된다. 즉 다수 캐리어에 의한 전류가 흐른다.

- 역방향 포화전류 : 각 영역의 소수 캐리어가 공핍 영역 경계면을 맍아 드리프트 전류성분을 만든다

- 순방향 포화전류 : 각 영역의 다수 캐리어가 이동하면서 확산 전류성분을 만든다.

- 1N4148 : 기본적인 실리콘 다이오드

클리핑 : 신호의 세기를 원하는 값으로 제한하는 것

클램핑 : 전압이 급격하게 변하려고 할 때, 변화를 제한하는 것

'전자회로 해석 및 설계' 카테고리의 다른 글

| 전자회로 해석 및 설계 7일차 (0) | 2023.05.19 |

|---|---|

| 전자회로 해석 및 설계 6일차 (0) | 2023.05.15 |

| 전자회로 해석 및 설계 3일차 L, C (0) | 2023.04.24 |

| 전자회로 해석 및 설계 2일차 (0) | 2023.04.21 |

| 전자회로 해석 및 설계 1일차 (0) | 2023.04.17 |