2023. 5. 19. 16:36ㆍ전자회로 해석 및 설계

ground를 분리할 때 (= 두 회로를 절연할 때) 사용

MOSFET

보통 MOSFET의 드레인 단자에 부하를 달아 놓는다. 이 때 Source단자의 전압이 가장 낮아야한다.

PMOS와 NMOS 차이

NMOS는 2.8V부터 전류가 흐르기 시작하고, Pmos는 3.6V부터 전류가 흐르기 시작한다. 이를 통해 PMOS의 문턱전압은 -3.6V, NMOS는 2.8V인 것을 알 수 있다. 또, 전류가 비선형적으로 오르는 것을 볼 수 있다.

좌측 NMOS의 D에 흐르는 전류는 5/1k = 5mA가 흘러야 한다. 초록색 파형을 보면 약 4.9934mA가 흐른다. 이 말은 MOSFET는 스위치로 동작할 때 양단의 전압 차이가 거의 없다는 특성을 가지고 있다. MOSFET는 파워소모가 적은 스위치라 볼 수 있다.

트랜지스터를 다른 모델로 변경한 모습이다. 현재 많이 쓰이는 모델로 변경하였다.

특성이 변한 모습을 볼 수 있다. Vth가 약 1.8V인 것처럼 보이는데, 실제 데이터시트는 아래와 같다.

데이터시트의 Vth는 1~2.5V 사이의 값을 가질 수 있다라고 나와 있다. 만약 회로를 구성할 때 시뮬레이션만 보고 2V를 걸어주었다면, 2.5V 문턱전압을 가지는 2n7002는 켜지지 않을 것이다. 따라서 마진을 좀 두어야한다.

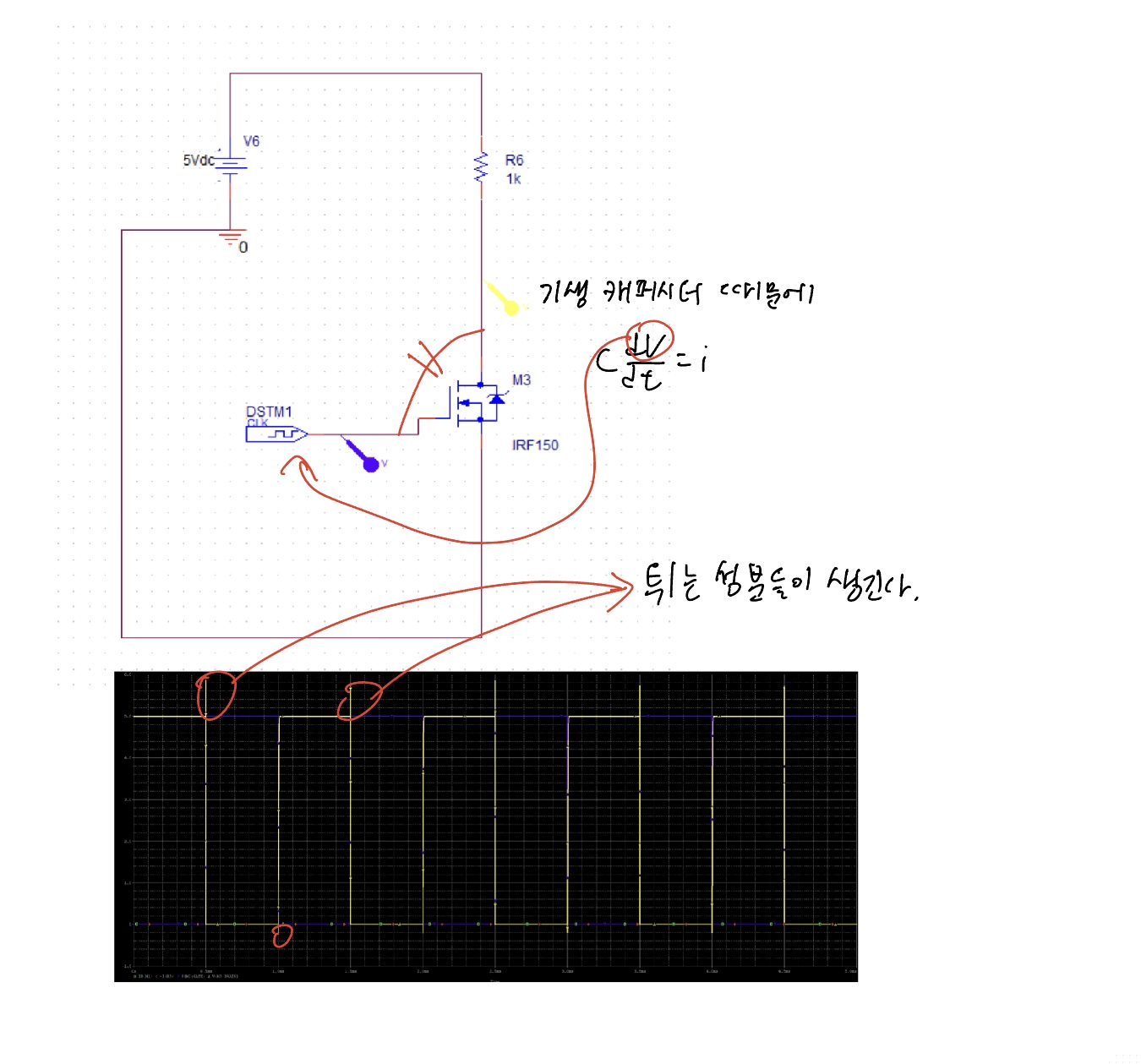

MosFET에는 기생 캐퍼시터가 매우 많다. 따라서 주파수 특성을 잡기 힘들다.

전압의 변화율을 줄여 전류를 줄여야 한다.

펄스를 RC회로에 통과시키면 시정수의 2.2배가 되는 Rising time, falling time이 생긴다.

게이트 단자 앞에 저항을 달면 이러한 노이즈가 줄어드는 것을 볼 수 있다. 저항이 너무 작으면 노이즈를 충분히 제거하지 못하고, M이상의 너무 큰 저항을 달면 딜레이가 생긴다. 보통 수k ~ 수십 k 사이의 값을 넣는다.

Control의 전압이 0이되면 Q1의 베이스 단자가 Open되어 전류가 흐르지 않는다.

Control의 전압이 5V가 돠면 Q1의 베이스 전류가 Q2를 통해 흐르고, Veb가 0.7V보다 커지며 I_Load가 통하게 된다.

이 구조의 단점은 파워 소모가 크다는 것이다. Main 스위치인 PNP트랜지스터에서 0.2V정도의 전압 강하가 발생하기 때문에 여기에서 파워 소모가 커지게 된다. 아래쪽 NPN은 PNP의 베이스 전류가 흐르기 때문에 전압강하가 발생해도 전력 소모는 크지 않다.

Mos 스위치의경우 BJT보다 비싸지만, 파워 소모는 거의 없다.

이때, 아래쪽 NMOS를 NPN트랜지스터로 교체하면 전력 소모는 크지 않지만, 가격은 더 저렴한 로드 스위치를 만들 수 있다. 이를 하이브리드 타입이라 한다.

또, PNP 또는 PMOS 하나만 사용하는 구조를 단순 구조라고 한다. 단순 구조를 사용할려면 Vin과 Control의 전압이 같아야 동작한다. 만약 Vin의 전압이 12V이고 Control의 전압이 5V라면 Control이 ON이든 OFF이든 상관없이 전류가 흘러 버린다.(VSG가 항상 Vth보다 크기 때문).

정리하자면 로드 스위치는 4가지 종류가 있는데, BJT, FET, 하이브리드, 단순 구조 가 있다. ]

출력이 잘 되는 것을 볼 수 있다. 하지만 Load가 IC의 입력 전원이라 생각하면, 병렬로 C가 달려 있을 것이다. 이 커패시터 때문에 In-rush-currnet가 발생되어 스위치와 커패시터가 모두 고장날 수 있다.

'전자회로 해석 및 설계' 카테고리의 다른 글

| 전자회로 해석 및 설계 6일차 (0) | 2023.05.15 |

|---|---|

| 전자회로 해석 및 설계 - 4일차 (0) | 2023.05.09 |

| 전자회로 해석 및 설계 3일차 L, C (0) | 2023.04.24 |

| 전자회로 해석 및 설계 2일차 (0) | 2023.04.21 |

| 전자회로 해석 및 설계 1일차 (0) | 2023.04.17 |